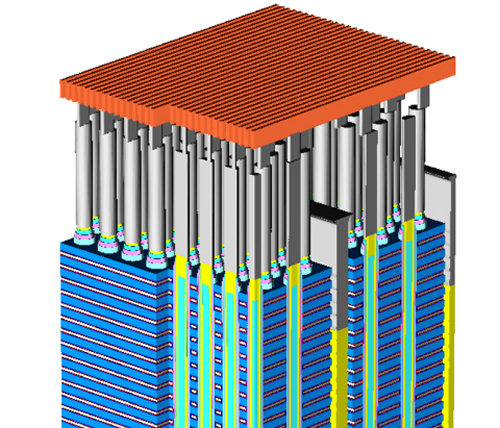

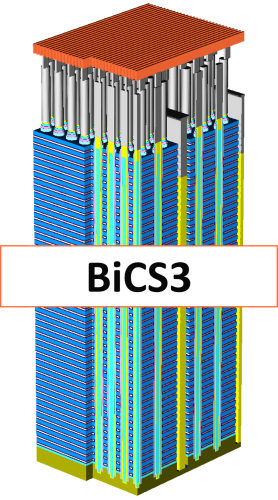

Western Digital hat heute die Entwicklung der nächsten Generation der 3D-NAND-Technologie, BiCS3, mit 64 Layern vertikaler Speichermöglichkeit angekündigt. Die Pilotproduktion der neuen Technologie hat in Japan begonnen. Erste Ergebnisse werden für Ende des Jahres erwartet.

Die Einführung der nächsten Generation der 3D-Nand-Technologie basiere auf einer neuen 64 Layer-Architektur, die von Western Digital entwickelt worden sein, erklärte Dr. Siva Sivaram, Executive Vice President, Memory Technology, Western Digital. «BiCS3 nutzt die 3-Bits-Pro-Zellen-Technologie sowie Vorteile durch hohe Seitenverhältnisse bei der Halbleiterherstellung, um eine höhere Kapazität, überragende Performance und Ausfallsicherheit zu niedrigen Kosten zu erreichen. Zusammen mit BiCS3 und BiCS2 hat sich unser 3D NAND Portfolio signifikant vergrössert, indem es uns ermöglicht, ein grosses Spektrum an Verbraucher-Anwendungen im Handel, für Mobility und in Rechenzentren zu erreichen.»

Die Einführung der nächsten Generation der 3D-Nand-Technologie basiere auf einer neuen 64 Layer-Architektur, die von Western Digital entwickelt worden sein, erklärte Dr. Siva Sivaram, Executive Vice President, Memory Technology, Western Digital. «BiCS3 nutzt die 3-Bits-Pro-Zellen-Technologie sowie Vorteile durch hohe Seitenverhältnisse bei der Halbleiterherstellung, um eine höhere Kapazität, überragende Performance und Ausfallsicherheit zu niedrigen Kosten zu erreichen. Zusammen mit BiCS3 und BiCS2 hat sich unser 3D NAND Portfolio signifikant vergrössert, indem es uns ermöglicht, ein grosses Spektrum an Verbraucher-Anwendungen im Handel, für Mobility und in Rechenzentren zu erreichen.»

BiCS3 wurde gemeinsam mit Western Digital’s Technologie- und Produktionspartner Toshiba in den Joint-Venture-Anlagen in Yokkaichi, Japan, entwickelt. Es wird zunächst mit einer Kapazität von 256 Gigabit eingesetzt und in einer Reihe von Kapazitäten bis zu einem halben Terrabit auf einem einzigen Chip verfügbar sein.

Western Digital erwartet die Auslieferung von BiCS3 für den Handel im vierten Quartal 2016. OEMs werden in diesem Quartal ausgestattet. Die vorhergehende Generation der 3D NAND Technologie, BiCS2, wird weiterhin an Verbraucher im Handel und bei OEMs ausgeliefert. Western Digital rechnet mit hohen Produktionsmengen der BiCS3 im ersten Halbjahr 2017.

Weitere Informationen finden Sie unter unter www.hgst.com, www.wd.com und www.sandisk.com.